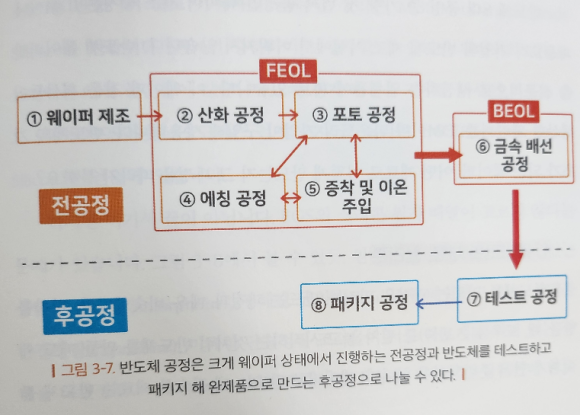

이제 8대공정의 마지막 ! 패키지공정까지 왔다. 짝짝짝👏🏻👏🏻👏🏻

마지막까지 화이팅. 아래는 반도체 후공정의 시작인 테스트공정에 대한 포스팅 링크이다.

"진짜 하루만에 이해하는 반도체 산업 " 이 책 강력추천 합니다 😊

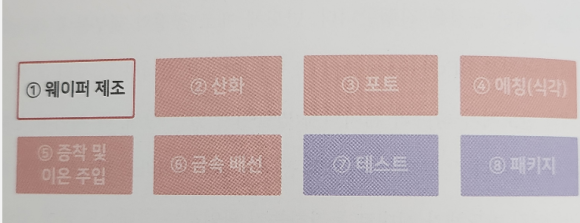

진짜 하루만에 이해하는 반도체 산업 - Part3 8대 공정 7. 테스트공정

8대공정이 거의 다 끝나간다. 이번 포스팅은 후공정인 테스트공정! 아래 링크는 금속배선공정에 대한 정리 포스팅이다. 😊 진짜 하루만에 이해하는 반도체 산업 - Part3 8대 공정 6. 금속배선공정

dudwolog.tistory.com

패키지공정 Package

1. 패키지공정이란 ?

이제 8대공정의 마지막 패키지공정이다. 단순 포장 과정이 아니라, 반도체 성능을 결정하는데 굉장히 중요한 역할을 한다. 패키지의 역할은 크게 세 가지이다.

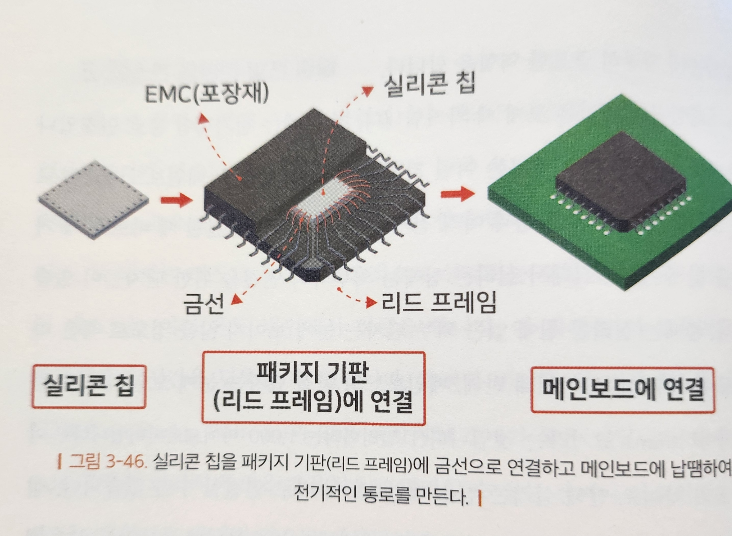

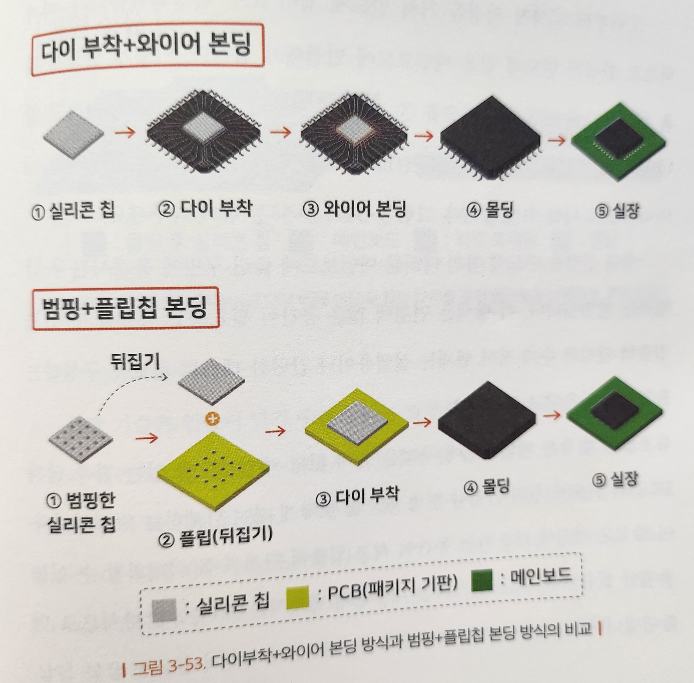

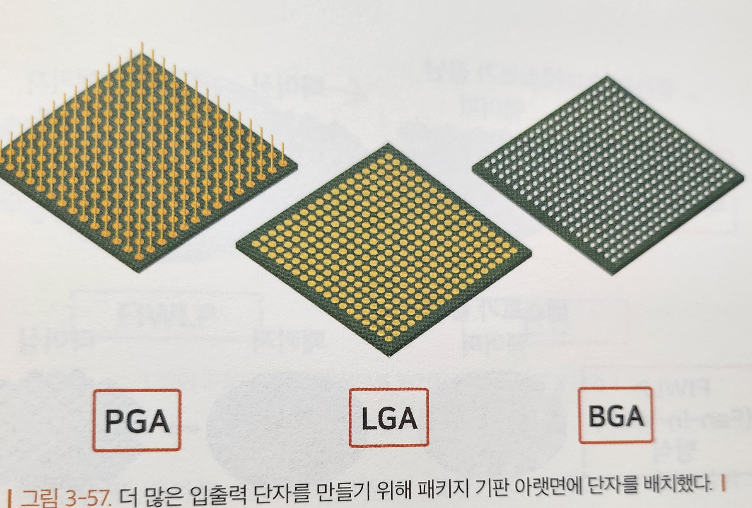

1. 전기적 통로 연결 : 실리콘 칩은 그 자체로는 어떤 기능도 할 수 없다. 메인보드 라고 부르는 초록색 판에 실리콘 칩과 여러 전기 소자들이 함께 연결될 때 비로소 제 기능을 할 수 있다. 그래서 실리콘 칩에는 외부와의 연결을 위한 단자들이 있다. 실리콘 칩에 있는 외부 단자는 아주 작은 마이크로미터 크기인데 반해, 메인보드의 연결 단자는 눈에 보일 정도로 큰 밀리미터 크기라는 것이 문제이다. 이런 크기 차이로 인해 실리콘 칩을 메인보드에 바로 연결할 수 없다. 이 둘 사이를 연결해 줄 매개체가 필요한 것이다. 이것이 바로 #패키지기관 이다. 패키지기관으로는 #리드프레임 (Lead Frame) 또는 #PCB 를 사용한다.

위 그림에서 알 수 있듯이, #금선 gold wire이 바로 실리콘 칩과 패키지 기판의 전기적인 연결 통로이다. 금선과 연결되어 있는 패키지 기관의 단자(리드프레임에 있는 수많은 다리)들이 그 역할을 한다. 이 단자들을 메인보드에 납땜하면,

실리콘칩<->패키지기관<->메인보드 사이에 전기적 통로가 연결된다. 위와 같은 방식 외에도 전기적연결통로를 만드는 방식은 더 다양하다.

실리콘칩의 성능이 아무리 좋아도 전기적인 통로가 효율적이지 않아 전기 신호가 늦게 전달된다면, 그 성능은 온전히 발휘될 수 없다. 반면, 칩의 성능 개선이 없어도 전기적인 통로를 더 효율적으로 만들면, 반도체 성능이 향상되는 것과 같은 효과가 있다. 어떻게 패키지를 하느냐에 따라 반도체 제품의 최종 성능이 결정되는 것이다. 실리콘 칩 자체의 성능 개선이 한계치에 다다른 상황에서 패키지 공정의 중요성이 커지고 있는 이유가 바로 여기에 있다.

2. 실리콘 칩의 보호 : 외부 충격으로 인한 파손, 장기간 습기에 노출 될 경우 화학적 변형이 발생해 반도체 특성이 달라질 수 있다. 그래서 실리콘 칩에 뚜껑을 덮어 외부 충격과 온도나 습도와 같은 외부 환경으로부터 칩을 보호하고 있다.

3. 효과적인 열 방출 : 실리콘 칩에 전력을 공급하면, 칩 안에 매우 미세한 전기적 연결통로들 간에 전기 신호가 오고가면서 어마어마한 열이 발생한다. 이 열을 제대로 방출하지 못하면, 기능에 문제가 생긴다. 그래서 패키지 공정을 통해 효과적으로 열이 방출되게끔 완제품의 형태를 설계하고 있다.

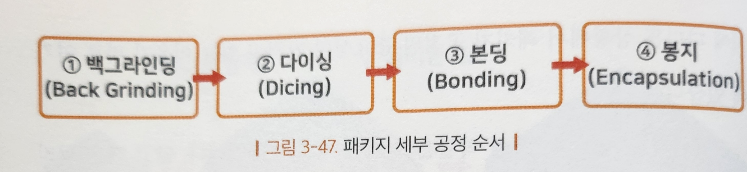

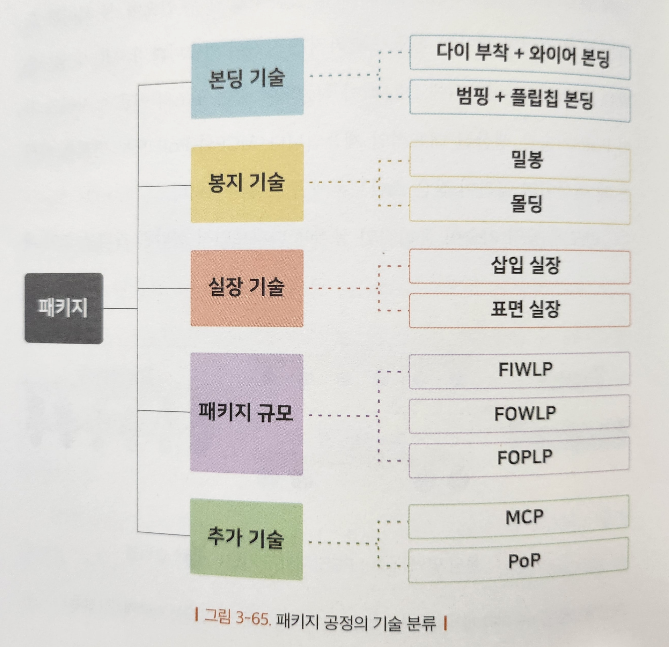

2. 패키지 세부 공정

- 백그라인딩 : 웨이퍼의 두께를 얇게 만듦. #backgriding

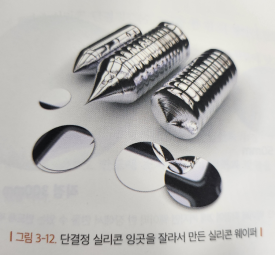

- 다이싱 : 웨이퍼를 낱개의 실리콘 칩으로 자르는 공정 #dicing

- 본딩 : 실리콘 칩을 패키지 기판에 얹고 전기적으로 연결하는 #bondling 공정

- 봉지 : 실리콘 칩과 전기적인 연결부를 보호하기 위해 포장재를 감싸는 공정 #encapsulation

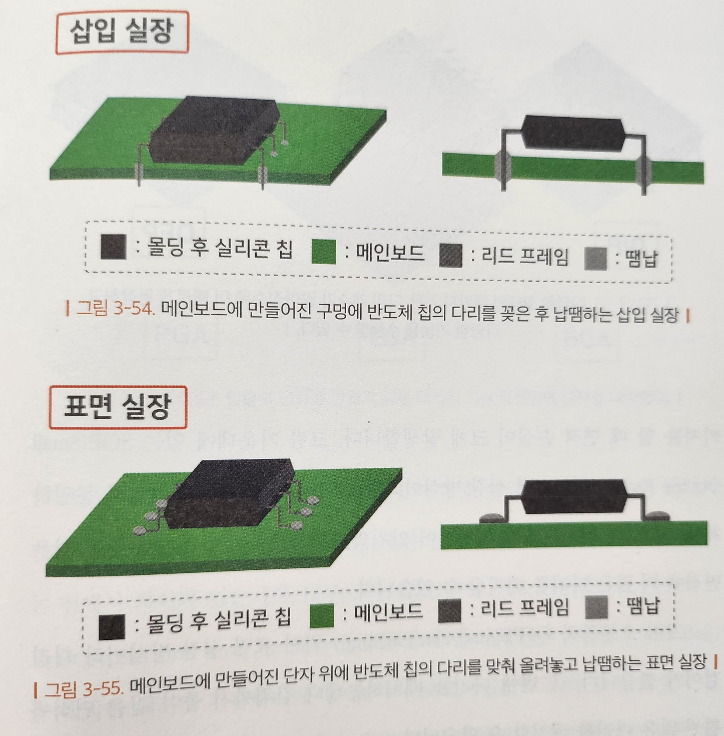

- 추가로 패키지가 모두 끝나면 반도체 완제품을 메인보드에 연결하는 #실장기술 #mounttechnology 이 필요하다.

한정된 공간에 더 많은 반도체 소자를 집적하기 위한 방법으로 트랜지스터 층을 층층이 쌓는 3D반도체 제품들이 제작되고 있다. 초창기에는 위의 그림 왼쪽과 같이 전통적인 본딩 방식을 활용하여 각 층마다 전기적인 연결을 만들어줬기 때문에 패키지 기관의 크기가 불필요하게 컸다.

이후 보다 효율적 연결을 위해 플립칩본딩 방식과 잘 맞는 실리콘관통전극 (TSV 공정)이 개발되었다. (Through Silicon Via). TSV는 건식에칭공정을 활용해 실리콘 칩들을 수직 관통하는 구멍을 뚫고, 그 안을 금속으로 채워 넣는 공정이다. 이 금속이 와이어의 역할을 대신한다.

그림의 오른쪽에서 볼 수 있듯이, 트랜지스터 층에 단자가 형성되고, 이 단자들이 새로운 본딩(범핑+플립칩 본딩)을 통해 패키지 기관의 금속 단자들과 바로 맞닿아 있어 전기신호가 이동하는 경로가 짧아 동작 속도가 매우 빠르다. 또한, 크기를 줄일 수 있다는 장점이 있다. 최근 트렌드인 3D반도체 소자를 본딩하는데 가장 부합하는 방식으로 TSV와 결합된 새로운 본딩 공정에 대해 연구가 진행되고 있다.

3. 공정규모에 따른 구분

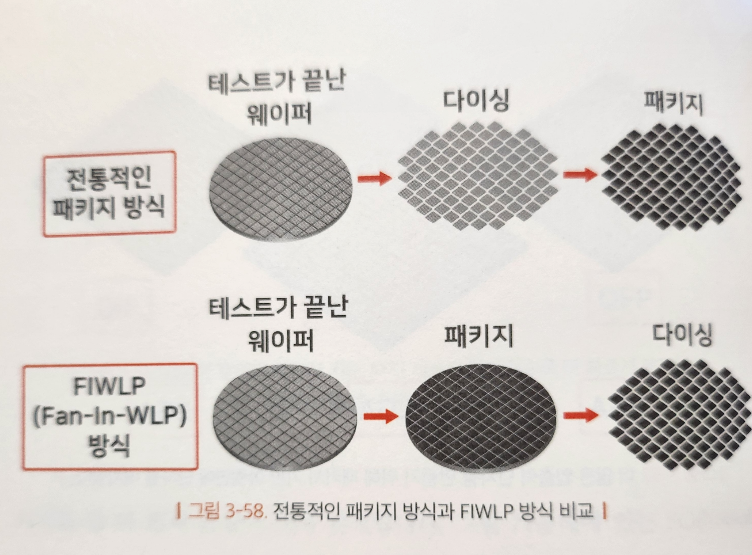

FIWLP Fan In Wafer Level Pacaking : 웨이퍼 상태에서 먼저 패키지를 한 후, 다이싱하는 팬인 웨이퍼규모패키지. 모든 공정이 처음부터 끝까지 한 덩어리의 웨이퍼 상태로 진행되기 때문에 공정연결성 이 좋다. 하지만, 불량칩들도 같이 패키지 되므로 공정에서 비용손실이 발생하며, 입출력 단자 수를 늘리는 데에 한계가 있다.

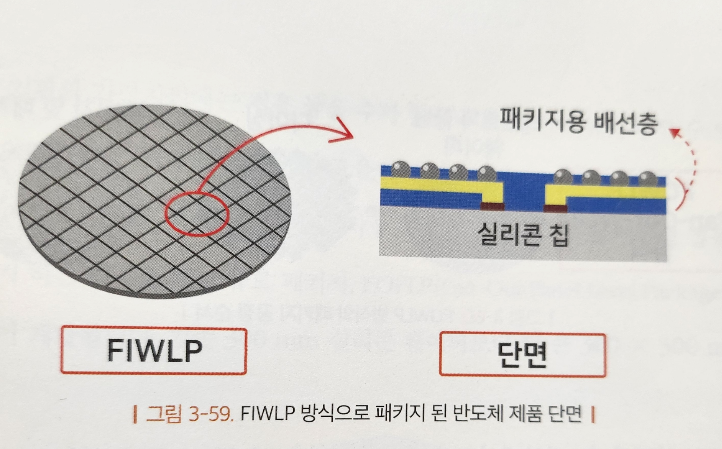

FIWLP단면 위 그림과 같이 패키지용 배선층 위에 입출력 단자인 솔더볼 이 총 8개가 형성되어 있다. 회색으로 표현된 실리콘 칩의 범위 안에서만 솔더볼을 형성할 수 있기 때문에 8개 이상은 만들 수가 없다. 그래서 FOWLP이 개발됨. 칩의 면적보다 더 큰 면적으로 연결 단자를 형성할 수 있는 팬아웃웨이퍼규모패키지 기법.

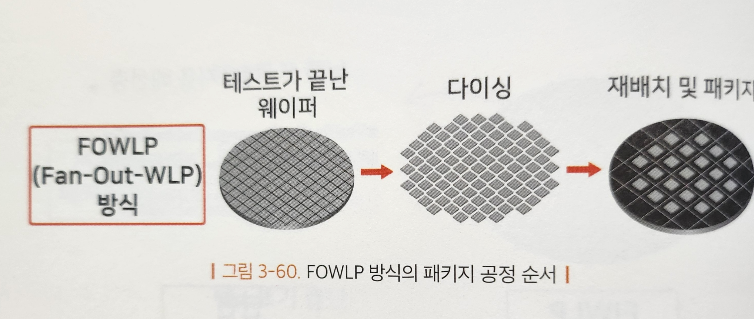

FOWLP Fan Out WLP : 웨이퍼 다이싱을 끝낸 뒤 양품인 실리콘 칩만을 별도로 선별한다. 선별된 칩들을 집착테이프가 부착된 캐리어기관(또 다른 실리콘 웨이퍼)에 일정 간격을 두고 재배치한다. 이 상태로 몰딩을 진행한 후, 접착테이프와 캐리어기판을 제거한다. 마지막으로 실리콘 칩의 면적보다 더 많은 면적에 입출력 단자를 형성할 수 있도록 #재분배층 RDL Re-Distribution Layer을 만들어준다.

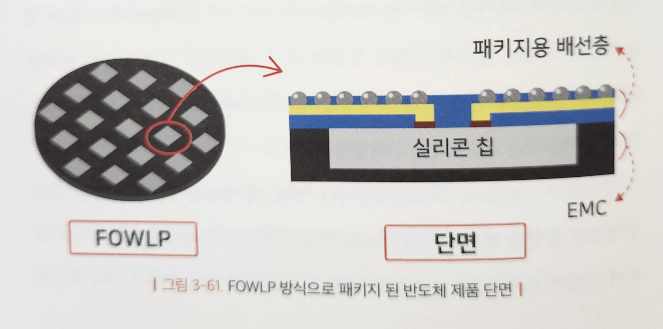

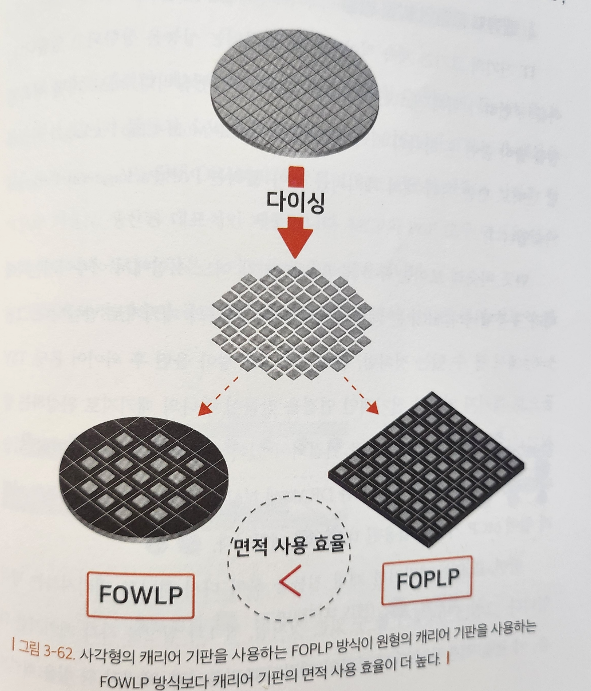

FOWLP단면: FOWLP은 FIWLP와 달리 양품만을 선별하기 때문에 비용손실을 줄일 수 있고, 실리콘 칩보다 더 큰 면적에 솔더볼을 형성할 수 있어 입출력 단자 수를 원하는 만큼 늘릴 수 있다는 장점을 가진다. 단점은, 칩 모양은 사각형인데 칩을 재배치 하는 캐리어 기판으로 사용된 웨이퍼는 원형이다. 모양이 서로 다르기 때문에 기판의 가장자리에는 칩을 놓을 수가 없다. 한번에 패키지 할 수 있는 칩의 수가 적어지는 만큼 패키지 효율이 떨어진다.

이를 해결 하기 위해 사각형 모양의 캐리어기판을 이용해 칩을 패키지 하는 #팬아웃패널규모패키지 #FOPLP FanOutPanelLevelPackage 기법이 개발된다.

기존 300mm 실리콘 웨이퍼보다 더 큰 300 x 300 mm2, 500 x 500 mm2, 600 x 600 mm2의 사각형 패널을 캐리어 기판으로 사용해 더 많은 수의 칩을 한 번에 패키지 할 수 있다. 하지만 사각형 패널용 공정 장비들을 따로 구비해야 하고, 사각형 모서리 쪽 공정 균일도가 떨어져 FOWLP대비 패키지 수율이 낮다는 단점이 있다.

4. 패키지 공정의 발전 방향

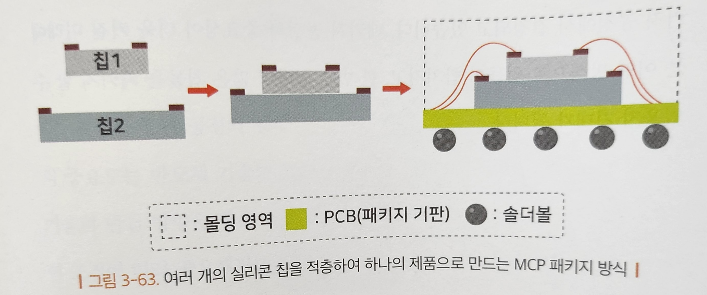

MCP Multi Chip Package 개별 실리콘 칩을 쌓아 올린 후 하나의 패키지로 만드는 MCP기술

삼성전자에서 발표한 DRAM과 NAND플래시메모리의 통합 메모리 칩이 MCP 기술이 활용된 대표적인 예이다.

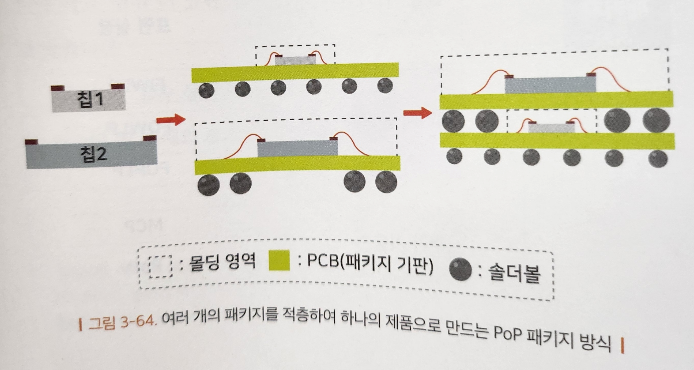

PoP (Package on Package) : 칩 단위로 만든 여러 개의 패키지를 쌓아 올리는 PoP기술. 패키지한 개별 칩들을 묶어 다시 하나로 패키지 하는 방식. 패키지 된 칩을 메인보드에 따로따로 연결할 때보다 차지하는 공간을 줄일 수 있으며, 둘 사이를 오가는 전선 길이가 짧아져 속도가 빨라지는 장점이 있다. TSMC가 생산을 맡은 로직(Logic : AP)위에 DRAM이 적층되어 있는 구조의 #애플 A시리즈 칩이 PoP 기술로 생산된 대표적인 제품이다.

MCP와 PoP모두 면적을 아끼는 게 핵심이며, 공간이 작은 스마트폰에 주로 활용된다.

'반도체공부' 카테고리의 다른 글

| 진짜 하루만에 이해하는 반도체 산업 - Part3 8대 공정 7. 테스트공정 (0) | 2023.09.14 |

|---|---|

| 진짜 하루만에 이해하는 반도체 산업 - Part3 8대 공정 6. 금속배선공정 (0) | 2023.09.14 |

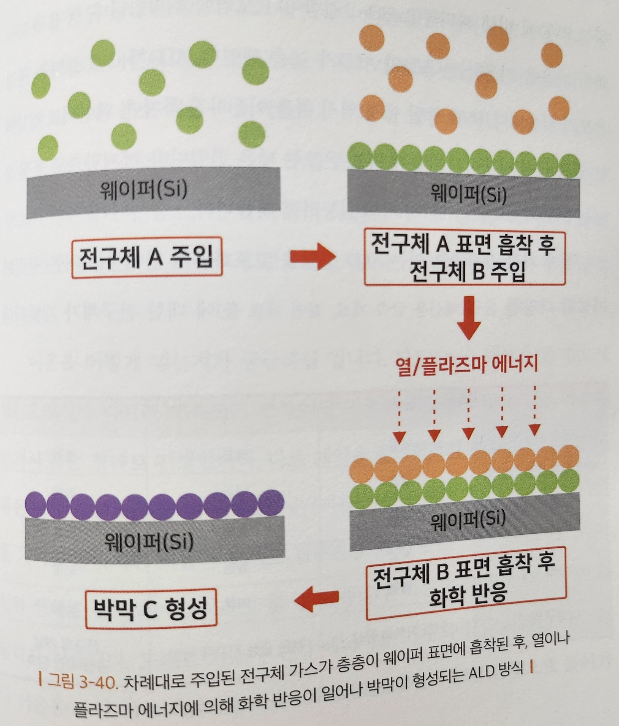

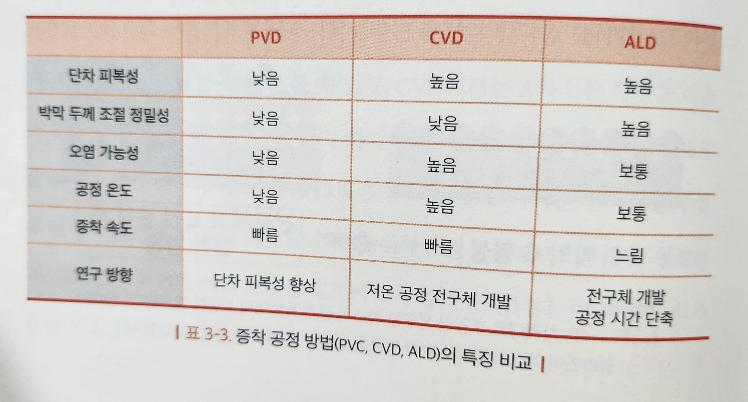

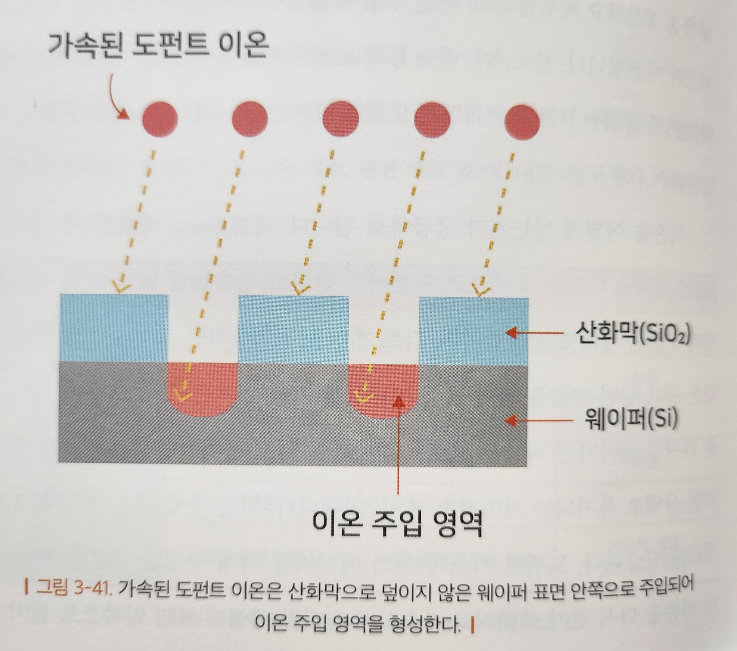

| 진짜 하루만에 이해하는 반도체 산업 - Part3 8대 공정 5. 증착공정 및 이온주입 공정 (1) | 2023.09.10 |

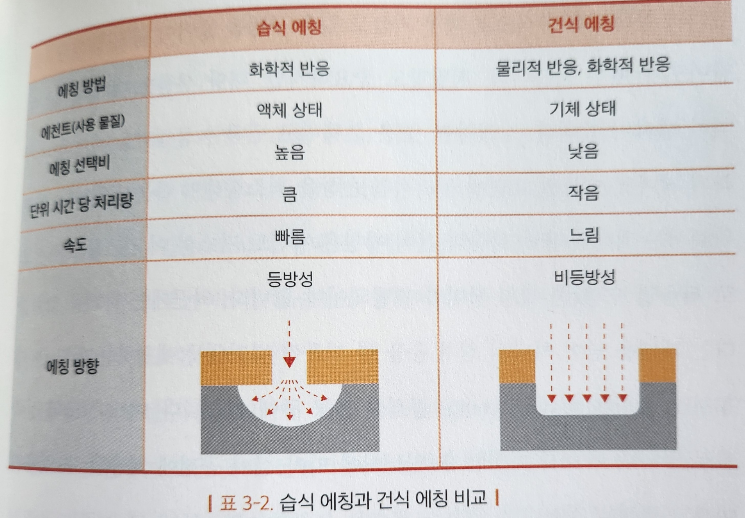

| 진짜 하루만에 이해하는 반도체 산업 - Part3 8대 공정 4. 에칭공정 (2) | 2023.09.09 |

| 진짜 하루만에 이해하는 반도체 산업 - Part3 8대 공정 3. 포토공정 (1) | 2023.09.06 |